Product Summary

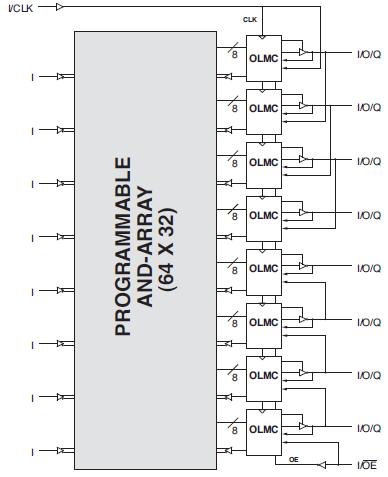

The GAL16V8D-25LPN is a High Performance E2CMOS PLD Generic Array Logic. It combines a high performance CMOS process with Electrically Erasable (E2) floating gate technology to provide the highest speed performance available in the PLD market. High speed erase times (<100ms) allow the GAL16V8D-25LPN to be reprogrammed quickly and efficiently. The generic architecture provides maximum design flexibility by allowing the Output Logic Macrocell (OLMC) to be configured by the user. An important subset of the many architecture configurations possible with the GAL16V8 are the PAL architectures listed in the table of the macrocell description section. The GAL16V8D-25LPN is capable of emulating any of these PAL architectures with full function/fuse map/parametric compatibility.

Parametrics

GAL16V8D-25LPN absolute maximum ratings: (1)Supply voltage VCC: –0.5 to +7V; (2)Input voltage applied: –2.5 to VCC +1.0V; (3)Off-state output voltage applied: –2.5 to VCC +1.0V; (4)Storage Temperature: –65 to 150℃; (5)Ambient Temperature with Power Applied: –55 to 125℃.

Features

GAL16V8D-25LPN features: (1)high performance E2CMOS technology: 3.5 ns Maximum Propagation Delay, Fmax = 250 MHz, 3.0 ns Maximum from Clock Input to Data Output, UltraMOS Advanced CMOS Technology; (2)50% to 75% reduction in power from bipolar: 75mA Typ Icc on Low Power Device, 45mA Typ Icc on Quarter Power Device; (3)active pull-ups on all pins; (4)E2 CELL technology: Reconfigurable Logic, Reprogrammable Cells, 100% Tested/100% Yields, High Speed Electrical Erasure (<100ms), 20 Year Data Retention.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

GAL16V8D-25LPN |

Lattice |

SPLD - Simple Programmable Logic Devices 16 Input 8 Output 5V Low Power 25ns |

Data Sheet |

|

|

||||||

|

GAL16V8D-25LPNI |

Lattice |

SPLD - Simple Programmable Logic Devices 16 INPUT 8 OUTPUT 5V LOW POWER 25ns |

Data Sheet |

|

|

||||||

(Hong Kong)

(Hong Kong)